【多线程与高并发原理篇:1_cpu多级缓存模型】

时间:2022-02-15 作者:father-of-little-pig

1. 背景

现代计算机技术中,cpu的计算速度远远高于主内存的读写速度。为了解决速度不匹配问题,充分利用cpu的性能,在cpu与主内存之间加入了多级缓存,也叫高速缓存,cpu读取数据直接从高速缓存中读取,写数据也类似,最后将数据从高速缓存同步到主内存。

2. cpu多级缓存模型

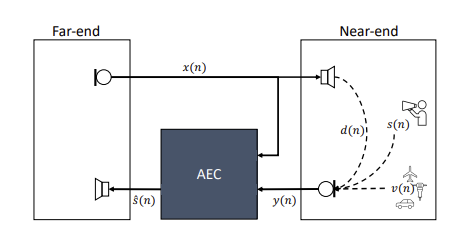

现代cpu多采用多核处理器机制,可以执行多个线程,每个cpu都有自己的高速缓存,读数据优先将主内存数据加载到高速缓存,然后cpu通过执行各自线程对应的指令,完成数据处理,处理完后再讲数据写入高速缓存,刷到主内存中,如下图所示:

3. 缓存数据一致性问题

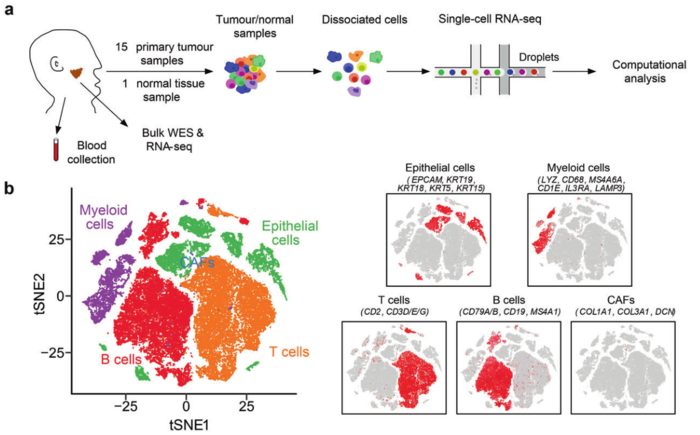

可以看出,各个cpu对应的高速缓存都拥有主内存的数据副本flg=1,并且各自独立,当cpu2对自己高速内存中的数据副本进行修改后,再次同步到主内存flg=2,cpu1对应高速缓存的数据副本与最新的主内存数据会出现不一致。如下图所示:

解决缓存数据不一致的方案将在下一篇分析!